J-Hub AI 분석: 글로벌 기술 심리 변화에 따른 고성능 컴퓨팅(HPC) 수요 사이클 분석 및 엔지니어링 로드맵 재조정 방안

제공 분석 주체: J-Hub AI 분석 시스템 분석 대상: 글로벌 증시 및 위험선호 심리 변화 (기술주 중심 흐름) 분석 목적: 반도체 엔지니어가 주목해야 할 산업 트렌드 및 기술적 기회 영역 식별

[Summary: 핵심 요약]

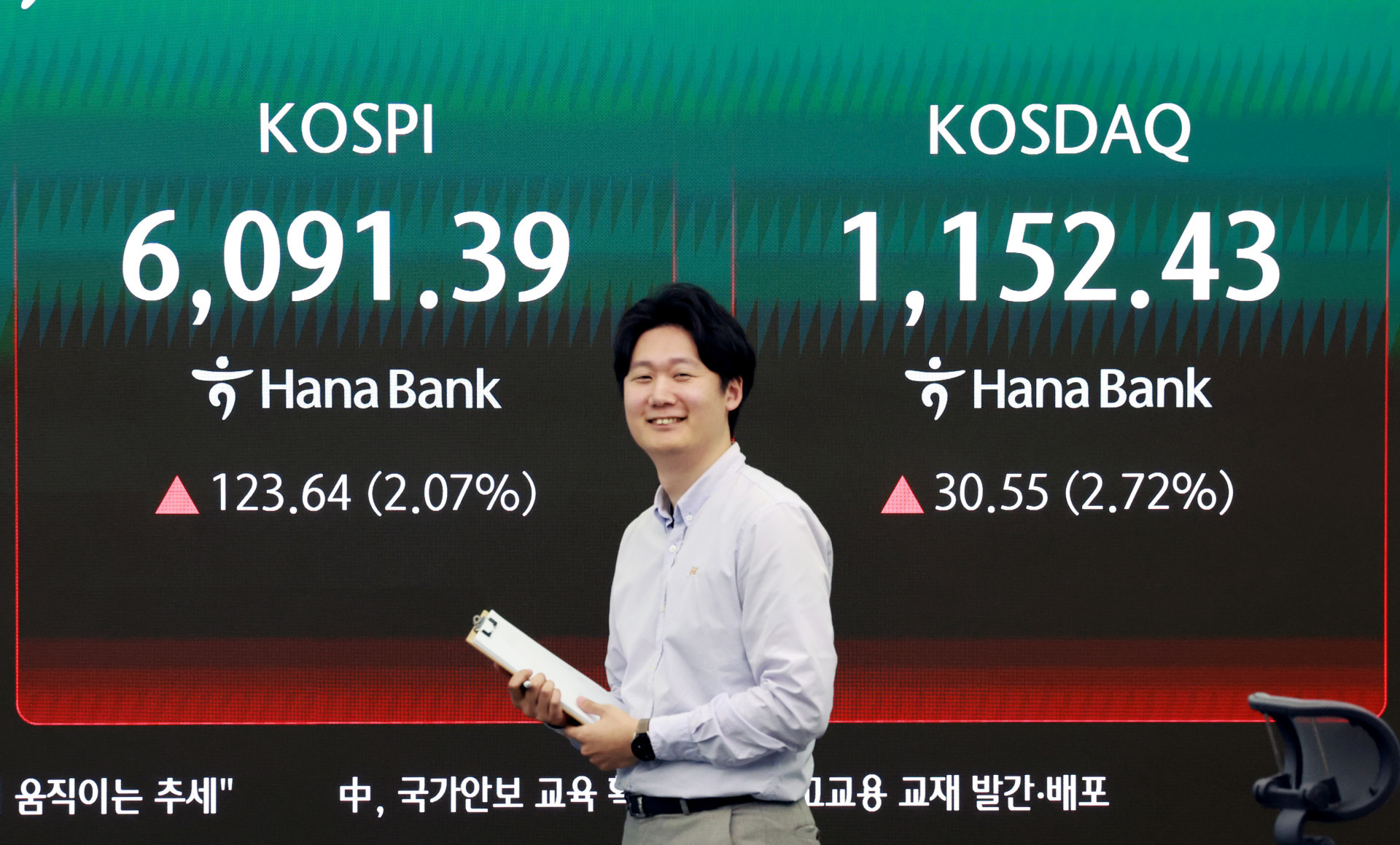

제공된 금융 시장 데이터는 글로벌 투자자들이 '위험선호 심리(Risk Appetite)'를 전반적으로 회복하고 있음을 명확하게 보여줍니다. 특히, 시장 상승을 견인하는 동력은 지정학적 불안정성 해소 기대와 함께 클라우드 컴퓨팅, 인공지능(AI), 그리고 고성능 컴퓨팅(HPC) 분야를 선도하는 주요 기술 기업들의 실적 전망에 집중되어 있습니다.

이는 단순한 자본 이동을 넘어, 차세대 AI 인프라 구축에 대한 전 세계적인 자본 투입 확대를 의미합니다. 반도체 관점에서 볼 때, 이는 DRAM/NAND 메모리 시장의 단기적인 수요 회복을 넘어, 고대역폭 메모리(HBM), 첨단 패키징 기술(Advanced Packaging), 그리고 초저전력/고효율 아키텍처를 요구하는 근본적인 수요 증폭 신호로 해석되어야 합니다.

[Technical Deep Dive: 기술적 세부 분석]

보고서가 관찰된 시장 흐름은 명확하게 ‘기술주 집중 현상’으로 나타납니다. S&P 500과 나스닥 지수의 사상 최고치 경신, 그리고 오라클, 마이크로소프트 등 주요 클라우드 및 AI 서비스 기업의 급등은 다음과 같은 기술적 요구사항을 내포하고 있습니다.

- 메모리 계층 구조의 진화 가속화: AI 워크로드(AI Workload)는 기존 CPU-RAM 구조를 초과하는 막대한 데이터를 초고속으로 처리할 것을 요구합니다. 이는 단순한 메모리 용량 증가가 아닌, 메모리 대 프로세서 간 데이터 전송 병목 현상(Data Bottleneck) 해결을 목표로 합니다. 따라서 HBM(High Bandwidth Memory) 및 이를 수용하는 인터페이스 설계 기술의 중요성이 극대화됩니다.

- 컴퓨팅 아키텍처의 분산 및 특화: 특정 범용 CPU 아키텍처에 의존하는 방식에서 벗어나, 텐서 처리 가속기(Tensor Processing Units, TPU)나 NPU(Neural Processing Units)와 같은 목적에 특화된 가속기(Accelerators) 중심으로 컴퓨팅 자원을 분산하는 추세가 지배적입니다. 이는 곧 반도체 설계 시 IP(Intellectual Property) 레벨의 다변화와 전문화를 요구합니다.

- 첨단 패키징의 필수화 (Advanced Packaging): 성능 향상의 한계에 도달한 단일 다이(Single Die) 구조의 한계를 극복하기 위해, 여러 개의 전문화된 칩을 하나로 통합하는 2.5D/3D 패키징 기술(e.g., CoWoS, Hybrid Bonding)이 사실상 필수 인프라가 되었습니다. 이는 설계, 공정, 테스트가 통합적으로 이루어지는 복합적인 엔지니어링 난제입니다.

[Market & Industry Impact: 산업 영향도]

시장 전반의 위험선호 심리 확산은 투자 주체들이 단기적인 시장 수익률보다는 장기적인 성장 동력(Growth Drivers)을 가진 산업 부문에 자본을 집중하겠다는 의지를 반영합니다.

- 클라우드 및 데이터센터 시장의 구조적 확대: 주요 빅테크 기업의 성장은 클라우드 인프라 증설을 필연적으로 요구하며, 이는 곧 막대한 양의 전력, 서버, 그리고 가장 핵심적으로 차세대 컴퓨팅 칩에 대한 구조적 수요 증가를 의미합니다.

- 지정학적 변수가 기술 투자로 전환: 전쟁 리스크 감소에 대한 기대는 글로벌 경제 활동 정상화 신호로 작용하며, 기업들이 연구개발(R&D) 투자를 미뤄왔던 핵심 기술(AI, 양자 컴퓨팅) 분야에 공격적으로 재배치하고 있음을 시사합니다.

- 양자 컴퓨팅 및 극한 컴퓨팅의 초기 시장 진입: 시장에서 급등한 일부 양자 컴퓨팅 관련 종목은, 아직 상용화 초기 단계에 있는 고위험 고수익(High-Risk, High-Reward) 분야에 자본이 유입되기 시작했음을 알려줍니다. 이는 향후 수년 내에 컴퓨팅 패러다임 자체를 변화시킬 잠재력을 가졌습니다.

[Engineering Perspective: 엔지니어링 인사이트]

반도체 엔지니어는 이러한 거시적 시장 트렌드를 다음의 세 가지 관점에서 설계 및 공정 혁신 과제로 접근해야 합니다.

1. I/O 인터페이스의 혁신적 설계: 현재 가장 시급한 병목 지점은 데이터 I/O입니다. 엔지니어는 HBM, CXL(Compute Express Link) 등 고속 인터커넥트 표준에 최적화된 인터페이스 설계와 신호 무결성(Signal Integrity) 확보에 중점을 두어야 합니다. 저전력 고속 데이터 전송을 위한 차세대 패키징 기법 연구가 핵심입니다.

2. 공정 기술의 다각화 및 결합: 단일 재료/공정만으로는 AI 시대의 요구를 충족할 수 없습니다. SiC, GaN 등의 화합물 반도체와 CMOS를 결합하는 이종 소자 통합(Heterogeneous Integration) 기술, 그리고 GAA(Gate-All-Around)와 같은 트랜지스터 구조의 혁신적인 적용이 요구됩니다. 특히, 패키징 레벨에서 성능을 끌어올리는 System-in-Package (SiP) 역량이 가장 중요한 경쟁력이 될 것입니다.

3. 전력 관리 시스템(Power Management): 고성능 컴퓨팅 칩은 전력 소모가 극심합니다. 따라서 프로세서-패키징 레벨에서 발생하는 열 문제를 근본적으로 해결할 수 있는 혁신적인 열 관리 소재(Thermal Interface Materials)와 전력 분배 아키텍처(Power Distribution Network) 설계가 엔지니어링의 최우선 과제입니다.

#반도체 #HPC #AI가속기 #고대역폭메모리 #첨단패키징 #기술분석 #시스템통합